# **Chorus SiT91213**

### Low Phase Noise MEMS Clock Generator

### Description

The Chorus SiT91213 is a low phase noise MEMS-based clock generator designed for low-power, low jitter applications. The device has a single clock domain and can drive up to 8 low-skew single-ended output loads or 4 low-skew differential loads.

The Chorus SiT91213 integrates an internal MEMS resonator as the frequency source for the internal PLL, eliminating the need for an external oscillator or resonator. The integrated MEMS improves system reliability by eliminating traditional clock generator's requirements for an external quartz and along with it, issues like activity dips due to shock and vibration and matching requirements.

The device is fully configurable in output frequency, clock output buffer type (differential and LVCMOS) and individual output enables, through the serial interface. Internal monitor flags and alarm conditions can be configured to be reported through GPIOs.

The device is compliant with PCle Generation 1-6.

User-defined, pre-programmed, and user-programmable NVM enables a high degree of flexibility and defined startup-configuration. Configurable GPIO pins support state changes such as individual output enable selection.

#### **Features**

- Standard Frequencies from 1 MHz to 700 MHz

- Fully integrated MEMS-based clock source

- Configurable clock domain and 4 differential outputs or 8 single-ended outputs

- Configurable output clock drivers:

- LVDS, HCSL, LVPECL, LVCMOS

- **Excellent frequency stability**

- ±20 ppm (-40°C to 105°C)

- o ±50 ppm (-40°C to 105°C)

- Configurable spread-spectrum clock generation

- Compliant with PCIe Generation 1 to 6

- Clock fault monitors (Lock Loss)

- Supply voltage of 1.8 V to 3.3 V

- Low phase jitter, 100 fs maximum (12 kHz-20 MHz)

- Resistant to shock/vibration

- Max. Operating range: -40°C to 105°C

- I<sup>2</sup>C or SPI serial interface for configuration

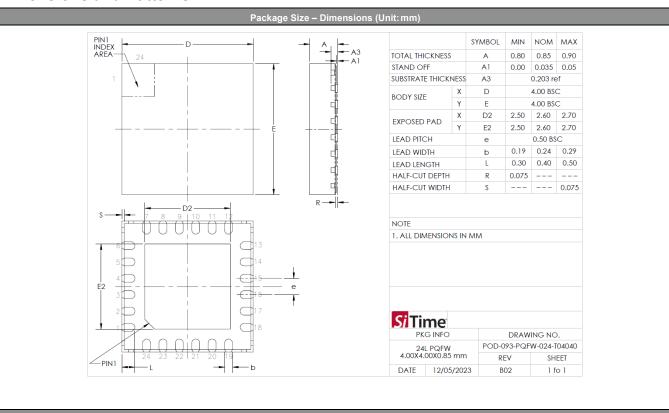

- QFN 24 pin 4 x 4 mm, 0.5 mm pitch (wettable flank) package

### **Applications**

- Datacenter, Switches, Smart NIC

- Wireless 5G infrastructure equipment

- High Speed Links: Ethernet, Optical

- High Speed Interconnect: PCIe and SerDes

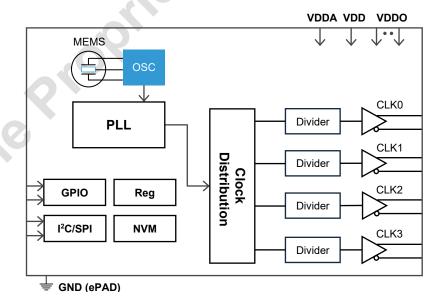

# **Block Diagram**

Figure 1. Chorus SiT91213 Block Diagram

# **Table of Contents**

| Description                                                                                           | 1           |

|-------------------------------------------------------------------------------------------------------|-------------|

| Features                                                                                              | 1           |

| Applications                                                                                          | 1           |

| Block Diagram                                                                                         | 1           |

| Ordering Information                                                                                  | 3           |

| Functional DescriptionError! Bookmark n                                                               | ot defined. |

| Chip Status MonitoringError! Bookmark n                                                               | ot defined. |

| General Purpose InputsError! Bookmark n                                                               | ot defined. |

| Electrical Characteristics                                                                            | 6           |

| FlexSwing Configurations                                                                              | 13          |

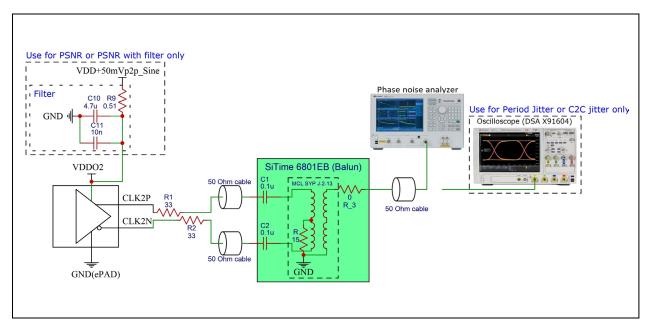

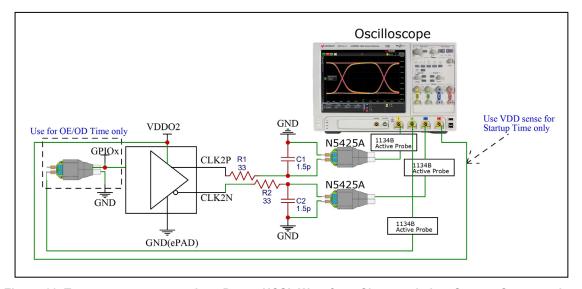

| Test Circuit Diagrams                                                                                 | 15          |

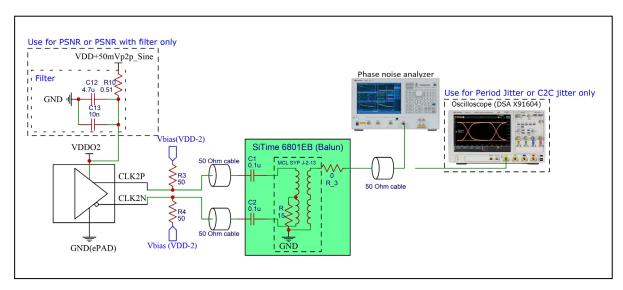

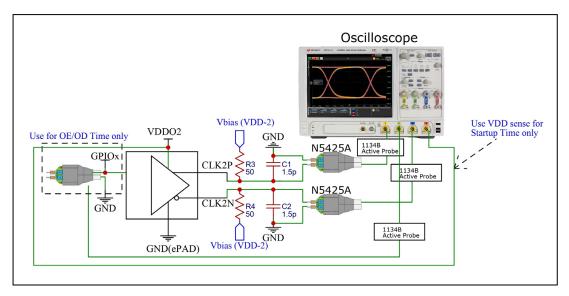

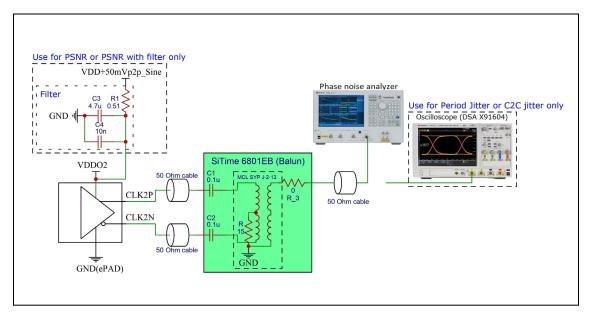

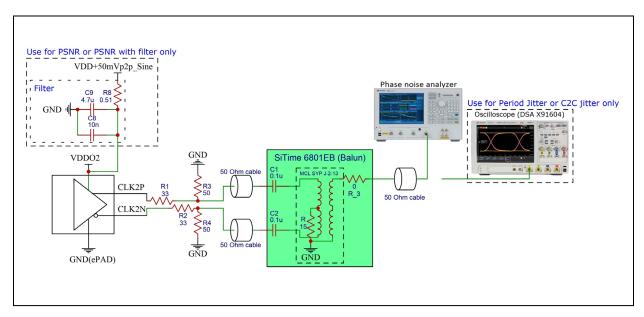

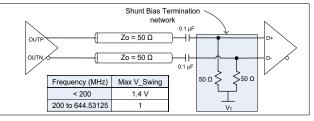

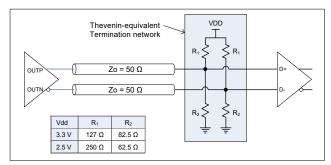

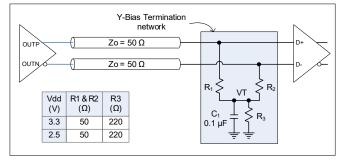

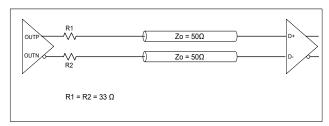

| Test Setups for LVPECL Measurements                                                                   | 15          |

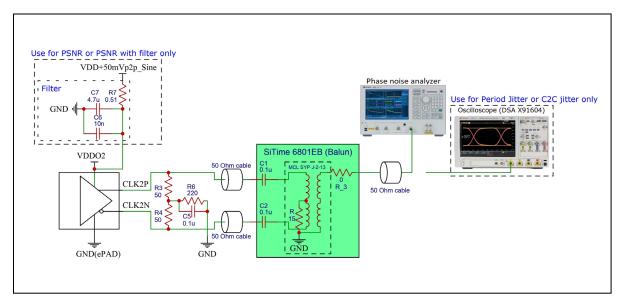

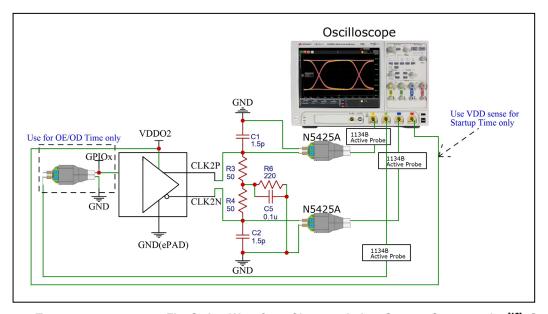

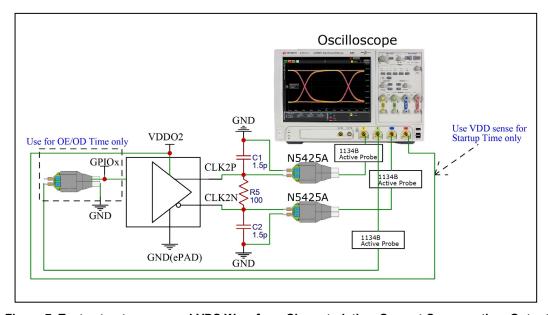

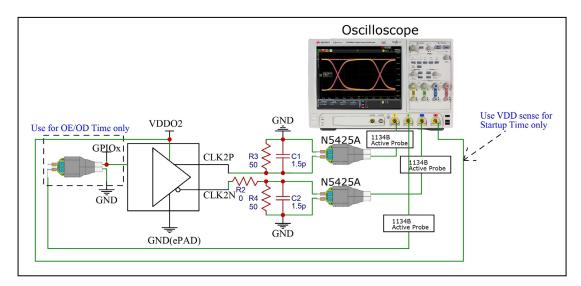

| Test Setups for FlexSwing Measurements <sup>[10]</sup>                                                | 16          |

| Test Setups for LVDS Measurements                                                                     | 17          |

| Test Setups for HCSL Measurements                                                                     |             |

| Test Setups for Low-Power HCSL Measurements                                                           |             |

| Naveform Diagrams                                                                                     | 20          |

| Termination Diagrams                                                                                  | 22          |

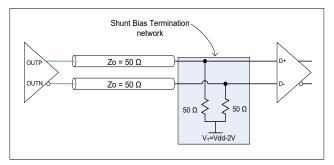

| LVPECL and FlexSwing Termination                                                                      |             |

| LVDS, Supply Voltage: 1.8 V ±5%, 2.5 V ±10%, 3.3 V ±10%, 2.25 V to 3.63 V, 1.71 V to 3.63 V           |             |

| HCSL, Supply Voltage: 1.8 V ±5%, 2.5 V ±10%, 3.3 V ±10%, 2.25 V to 3.63 V, 1.71 V to 3.63 V           |             |

| Low-power HCSL, Supply Voltage: 1.8 V ±5%, 2.5 V ±10%, 3.3 V ±10%, 2.25 V to 3.63 V, 1.71 V to 3.63 V | 23          |

| Operating Temperature and Thermal Characteristics                                                     | 24          |

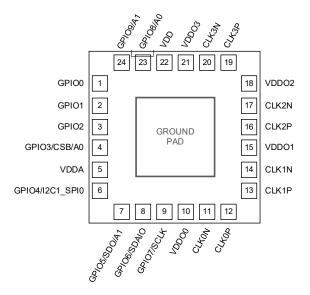

| Package Pin-Out and Description (Preliminary)                                                         | 26          |

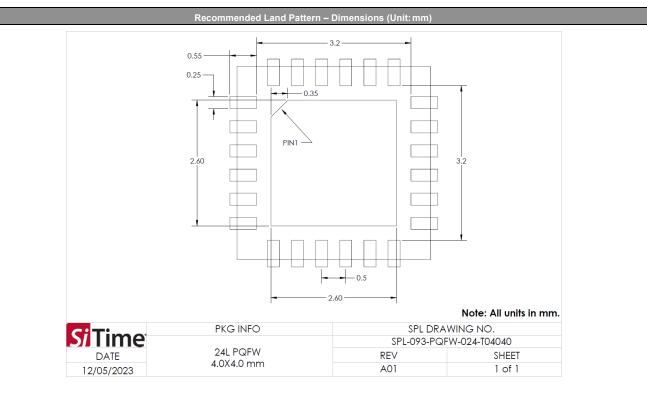

| Dimensions and Patterns                                                                               | 28          |

| Additional Information                                                                                | 29          |

| Revision History                                                                                      | 30          |

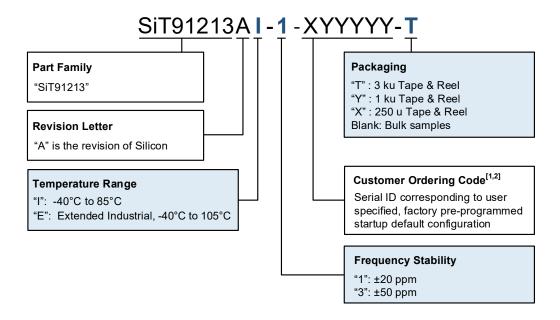

# **Ordering Information**

#### Notes:

- 1. X = "A" and "B" customer device, "C to "Z" reserved.

- A: Denotes blank devices;

- B: Denotes Pre-configured devices, contact SiTime for the specifics.

- 2. Y = 0..9, A...Z for custom serial ID.

### **Functional Description**

The Chorus SiT91213 is a commercial grade, low-jitter clock generator with an integrated SiTime MEMS resonator targeting applications in the Communications, Enterprise and Industrial segments. The Chorus SiT91213 can provide 4 configurable differential or 8 single-ended low skew outputs, or a combination of both. Differential outputs can be configured up to a maximum clock frequency of 700 MHz, while single ended outputs can be configured up to a maximum clock frequency of 220 MHz. The integrated MEMS resonator enables the Chorus SiT91213 to be operated without an external quartz crystal or oscillator reference, thereby eliminating the need for associated matching requirements.

The output drivers support commonly used signal formats, such as LVPECL, LVDS, HCSL, LVCMOS, as well as FlexSwing. Individual VDDO pins capable of accepting between 1.8 V and 3.3 V are available for each differential output driver, The core voltage supply (VDD, VDDA) accepts 3.3 V, 2.5 V, or 1.8 V and is independent from the output supplies (VDDO).

The SiT91213 combines SiTime's highly reliable MEMS resonator with a wideband PLL, on-chip temperature compensation, and four integer dividers to generate high-performance outputs with typical jitter of 70 fs and frequency stability of ±20 ppm or ±50 ppm across the wide temperature range, -40°C to 105°C. The Chorus SiT91213's on-chip regulators ensure extremely good power supply noise rejection, ensuring minimal deviation from the jitter specification due to power supply noise.

The elimination of an external reference clock source leads to improved ease of use by eliminating the need for any matching or frequency jump issues. Importantly for mission critical applications, all dependence on quartz crystals (which have been shown to be prone to high failure rates) is eliminated. In addition to improved failure rates, internal functions such as the MEMS reference clock, bandgap reference, PLL, and VDDIOs, and output drivers are monitored. This is a significant improvement over common on-chip status monitors in clock generator chips. Fault conditions on these monitored functions can be configured

to be sent out to GPIO outputs individually or as a combined alarm signal or read via I<sup>2</sup>C or SPI interface. This allows an external MCU to be alerted to a fault condition in the clock generator to take appropriate action consistent with system requirements.

The Chorus SiT91213 is available optionally with or without a serial interface (I²C or SPI). The serial interface can be used to read internal registers, including status of the internal monitoring functions. A user can use In-System Configuration (ISC) mode to write to contents of internal registers to modify the device configuration via the serial interface. In such a use case, the modified configuration will be lost at the next power cycle. The Chorus SiT91213 allows the user to burn the new configuration into the NVM via the In-System Programming (ISP) Mode, which will then be the new default configuration at the next power cycle.

Optionally, the user can store up to four different static clock configurations in the Chorus SiT91213 NVM, one of which is selectable at power-up based on the status sampled on the two Frequency Select pins. The four static configurations cannot be modified using ISP mode, but ISC mode can still be used to modify internal register contents.

For applications which require only a standard configuration, the Chorus SiT91213 is also available as a factory configured device without a serial interface, which allows the use of the serial interface pins as additional GPIOs. SiTime will program the NVM to configure the devices according to specific customer requirements.

The SiT91213 also supports Digitally Controlled Oscillator (DCO) Mode in which the user can modulate the output frequencies via serial interface (I2C/SPI). The user can control two registers which modulate the internal Voltage Controlled Oscillator (VCO) in the PLL. All enabled outputs will change simultaneously in response to the VCO update. The VCO tuning range is +/- 800ppm with an increment or decrement step size of 0.023 ppt. This can be achieved by writing to a 36-bit DCO tuning register. A second 20-bit register allows the user to limit or clip the tuning range to less than +/- 800ppm. The clipped tuning range can be set with a step size of 0.753 ppb.

# **Chip Status Monitoring**

The SiT91213 monitors multiple internal parameters and makes these status monitoring functions available to an external MCU via GPIO pins or through direct access of internal registers via I<sup>2</sup>C/SPI. All the status signals. listed in the table below, are also accessible via register reads over the serial interface (I<sup>2</sup>C or SPI).

**Table 1. Status Monitoring Signals**

| Monitoring Function          | Monitored on GPIO Pin<br>(Parts without I <sup>2</sup> C/SPI) | Monitored on GPIO Pin<br>(Parts with I <sup>2</sup> C/SPI) | Function                                                                                                                         |  |  |  |  |  |  |

|------------------------------|---------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MEMS Clock Monitor           | Pin 2 / 3 / 4 / 6 / 7 / 23 / 24                               | Pin 2 / 3 / 23 / 24                                        | Goes low when internal MEMS clock does not oscillate                                                                             |  |  |  |  |  |  |

| Bandgap Monitor              | Pin 2 / 3 / 4 / 6 / 7 / 23 / 24                               | Pin 2 / 3 / 23 / 24                                        | Goes low when internal band gap reference falls below threshold                                                                  |  |  |  |  |  |  |

| PLL Lock Monitor             | Pin 2 / 3 / 4 / 6 / 7 / 23 / 24                               | Pin 2 / 3 / 23 / 24                                        | Goes low when PLL loses lock with MEMS reference clock                                                                           |  |  |  |  |  |  |

| Clock0 Ready                 | Pin 2                                                         | Pin 2                                                      | Goes low when Clock0 driver is not toggling / has a fault                                                                        |  |  |  |  |  |  |

| Clock1 Ready                 | Pin 3                                                         | Pin 3                                                      | Goes low when Clock1 driver is not toggling / has a fault                                                                        |  |  |  |  |  |  |

| Clock2 Ready                 | Pin 23                                                        | Pin 23                                                     | Goes low when Clock2 driver is not toggling / has a fault                                                                        |  |  |  |  |  |  |

| Clock3 Ready                 | Pin 24                                                        | Pin 24                                                     | Goes low when Clock3 driver is not toggling / has a fault                                                                        |  |  |  |  |  |  |

| Clock01 Ready                | Pin 6                                                         | -                                                          | Goes low when Clock0 or Clock1 driver are not toggling / have a far                                                              |  |  |  |  |  |  |

| Clock23 Ready                | Pin 7                                                         | -                                                          | Goes low when Clock2 or Clock3 driver are not toggling / have a fault                                                            |  |  |  |  |  |  |

| VDDO0 Good                   | Pin 2                                                         | Pin 2                                                      | Goes low when VDDO0 supply is below NVM-configured threshold                                                                     |  |  |  |  |  |  |

| VDDO1 Good                   | Pin 3                                                         | Pin 3                                                      | Goes low when VDDO1 supply is below NVM-configured threshold                                                                     |  |  |  |  |  |  |

| VDDO2 Good                   | Pin 23                                                        | Pin 23                                                     | Goes low when VDDO2 supply is below NVM-configured threshold                                                                     |  |  |  |  |  |  |

| VDDO3 Good                   | Pin 24                                                        | Pin 24                                                     | Goes low when VDDO3 supply is below NVM-configured threshold                                                                     |  |  |  |  |  |  |

| All Clocks Ready             | Pin 2 / 3 / 4 / 6 / 7 / 23 / 24                               | Pin 2 / 3 / 23 / 24                                        | Goes low when any enabled clock output is not toggling / has a fault                                                             |  |  |  |  |  |  |

| Alarm_B                      | Pin 2 / 3 / 4 / 6 / 7 / 23 / 24                               | Pin 2 / 3 / 23 / 24                                        | Goes low when any fault is triggered                                                                                             |  |  |  |  |  |  |

| ISP_Burn_Success             | Pin 4                                                         | (Access via register read)                                 | Asserted when in-system NVM burn is successful                                                                                   |  |  |  |  |  |  |

| VDDO01 Good                  | VDD001 Good Pin 6                                             |                                                            | Asserted when VDDO0 and VDDO1 are above user configured thresholds                                                               |  |  |  |  |  |  |

| VDDO23 Good                  | Pin 7                                                         | -                                                          | Asserted when VDDO2 and VDDO3 are above user configured thresholds                                                               |  |  |  |  |  |  |

| Die Temperature Out of Range | Accessible via reg                                            | jister reads only                                          | Asserted if die temperature is outside user-configured range.  Available via direct register access through I <sup>2</sup> C/SPI |  |  |  |  |  |  |

### **General Purpose Inputs**

Table 2. User Configurable Input Signals<sup>[3]</sup>

| Input Function  | Mapped on GPIO Pin<br>(Parts w/o I <sup>2</sup> C/SPI) | Mapped on GPIO Pin<br>(Parts with I <sup>2</sup> C) | Mapped on GPIO Pin<br>(Parts with SPI) | Function                                                                 |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------|-----------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| SSEN / SSEN     | Pin 1 / 3 / 4 / 8                                      | Pin 1 / 3 / 4                                       | Pin 1 / 3                              | Spread Spectrum enabled on all outputs (configurable active high or low) |  |  |  |  |  |  |

| OE0 / OE0       | Pin 2 / 3                                              | Pin 2 / 3                                           | Pin 2 / 3                              | Enable Output 0 (configurable active high or low)                        |  |  |  |  |  |  |

| OE1 / OE1       | Pin 2 / 3                                              | Pin 2 / 3                                           | Pin 2 / 3                              | Enable Output 1 (configurable active high or low)                        |  |  |  |  |  |  |

| OE2 / OE2       | Pin 1 / 6 / 7                                          | Pin 1 / 6 / 7                                       | Pin 1 / 6                              | Enable Output 2 (configurable active high or low)                        |  |  |  |  |  |  |

| OE3 / OE3       | Pin 1 / 6 / 7                                          | Pin 1 / 6 / 7                                       | Pin 1 / 6                              | Enable Output 3 (configurable active high or low)                        |  |  |  |  |  |  |

| OE_all / OE_all | Pin 2 / 7                                              | Pin 2 / 7                                           | Pin 2                                  | Enable all Outputs (configurable active high or low)                     |  |  |  |  |  |  |

| FS0             | Pin 9 / 23 Pin 23                                      |                                                     | Pin 23                                 | Frequency Select 0                                                       |  |  |  |  |  |  |

| FS1             | Pin 8 / 24                                             | Pin 24                                              | Pin 24                                 | Frequency Select 1                                                       |  |  |  |  |  |  |

#### Note:

3. The I<sup>2</sup>C and SPI pins can be reconfigured, in factory, as GPIO pins. Such parts (without the I<sup>2</sup>C or SPI interface) can be ordered directly only from SiTime.

## **Power Supply Sequencing**

The core power supplies (VDDA and VDD) are required to be at the same voltage. VDDOx can be chosen independently as required by the clock receiver. All VDDOx can be sequenced independently of each other and VDD/VDDA. However, VDD and VDDA should be brought up together.

### **Electrical Characteristics**

All Min and Max limits in the Electrical Characteristics tables are specified over operating temperature and rated operating voltage with standard output termination shown in the termination diagrams. Typical values are at 25°C and nominal supply voltage. See Test Circuit Diagrams for the test setups used with each signaling type.

Table 3. Electrical Characteristics - Common to All Output Signaling Types

| Parameter                                 | Symbol               | Min.   | Тур.     | Max.                  | Unit        | Condition                                                                                                                                                        |  |  |  |  |  |

|-------------------------------------------|----------------------|--------|----------|-----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                           |                      |        |          | Frequency Ra          | ange        |                                                                                                                                                                  |  |  |  |  |  |

| 0.1.15                                    | f                    |        |          | 700                   | MHz         | Differential clock outputs                                                                                                                                       |  |  |  |  |  |

| Output Frequency Range                    | f                    |        |          | 220                   | MHz         | Single-ended (LVCMOS) clock outputs                                                                                                                              |  |  |  |  |  |

|                                           |                      |        |          | Frequency Sta         | ability     |                                                                                                                                                                  |  |  |  |  |  |

|                                           |                      | -      | -        | ±20                   | ppm         | Inclusive of initial tolerance, operating temperature -40°C to                                                                                                   |  |  |  |  |  |

| Frequency Stability                       | F_stab               | _      | _        | ±50                   | ppm         | 105°C, rated power supply voltage, load variation of 2 pF ± 10 and 10 years aging at 85°C                                                                        |  |  |  |  |  |

|                                           |                      |        |          | Temperature F         | Sange       | and 10 years aging at 65 C                                                                                                                                       |  |  |  |  |  |

|                                           |                      | -40    | _        | +85                   | °C          | Industrial, ambient temperature                                                                                                                                  |  |  |  |  |  |

| Operating Temperature Range               | T_use                | -40    | _        | +105                  | °C          | Extended industrial, ambient temperature                                                                                                                         |  |  |  |  |  |

|                                           | l l                  | 10     | I        | Supply Volta          |             | Extended industrial, difficient temporature                                                                                                                      |  |  |  |  |  |

|                                           |                      | 1.71   | 1.80     | 1.89                  | V           | Voltage-supply order code "18". Contact SiTime for 1.5 V                                                                                                         |  |  |  |  |  |

| Supply Voltage                            | -                    | 2.25   | 2.50     | 2.75                  | V           | Voltage-supply order code "25"                                                                                                                                   |  |  |  |  |  |

| cupply relage                             | -                    | 2.97   | 3.30     | 3.63                  | V           | Voltage-supply order code "33"                                                                                                                                   |  |  |  |  |  |

|                                           | l l                  | 2.01   | 0.00     | Core Curre            |             | Tonago cappiy craci codo co                                                                                                                                      |  |  |  |  |  |

| Core Current                              | ldd                  | -      | _        | 55                    | mA          | Total current consumed on the VDD and VDDA power domains                                                                                                         |  |  |  |  |  |

| COLO GUITOIN                              | iuu                  |        | I        | Input Characte        | l .         | Total current consumed on the VBB and VBB/(power demand                                                                                                          |  |  |  |  |  |

| Input Voltage High                        | VIH                  | 70%    | _        | _                     | Vdd         | Logic High function for all input pins                                                                                                                           |  |  |  |  |  |

| Input Voltage Low                         | VIL                  | _      | _        | 30%                   | Vdd         | Logic High function for all input pins                                                                                                                           |  |  |  |  |  |

| put roimge zon                            |                      |        |          | Output Charact        | l .         | 20g.c r ng. r tancaser for an inpact pinto                                                                                                                       |  |  |  |  |  |

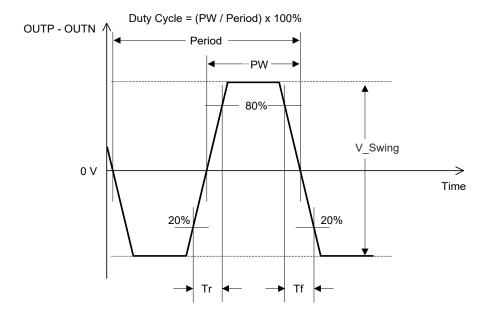

| Duty Cycle                                | DC                   | 45     | _        | 55                    | %           | See Figure 13 for waveform                                                                                                                                       |  |  |  |  |  |

|                                           |                      |        | Sta      | artup, OE and S       |             |                                                                                                                                                                  |  |  |  |  |  |

| Startup Time                              | T start              | _      | 1.2      | 2                     | ms          | Measured from the time Vdd reaches its rated minimum value                                                                                                       |  |  |  |  |  |

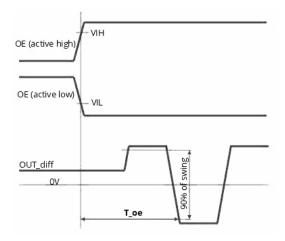

| Output Enable Time                        | T_oe                 | -      | -        | 600+1 clock<br>cycles | ns          | For all signaling types. Measured from the time OE pin toggles to enable logic level to the time clock pins reach 90% of final swing. See Figure 19 for waveform |  |  |  |  |  |

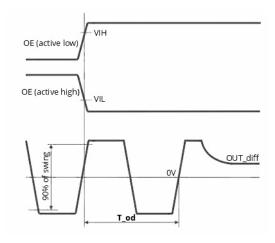

| Output Disable Time                       | T_od                 | -      | -        | 600+1 clock<br>cycles | ns          | Measured from the time OE pin toggles to disable logic level to the last clock edge. See Figure 20 for waveform                                                  |  |  |  |  |  |

|                                           |                      | Jitter | and Phas | e Noise, meası        | ured at f = | = 156.25 MHz                                                                                                                                                     |  |  |  |  |  |

| RMS Phase Jitter ("4-16A")                | T_phj                | -      | 55       | -                     | fs          | "4-16A" 4 MHz to 16 MHz offset frequency integration bandwidth with aliasing                                                                                     |  |  |  |  |  |

| RMS Phase Jitter (random)                 | T_phj                | _      | 70       | 100                   | fs          | 12 kHz to 20 MHz offset frequency integration bandwidth.                                                                                                         |  |  |  |  |  |

| Spurious Phase Noise                      | T_spn                | _      | -        | -95                   | dBc         | 12 kHz to 20 MHz offset frequency range                                                                                                                          |  |  |  |  |  |

| RMS Period Jitter <sup>[4]</sup>          | T_jitt_per           | -      | 0.5      | 0.6                   | ps          | Measured based on 10K cycle                                                                                                                                      |  |  |  |  |  |

| Peak Cycle-to-cycle Jitter <sup>[4]</sup> | T_jitt_cc            | _      | 3.5      | 6.2                   | ps          | Measured based on 1K cycle                                                                                                                                       |  |  |  |  |  |

|                                           |                      |        | Syn      | chronization ar       | nd Timing   |                                                                                                                                                                  |  |  |  |  |  |

| Output Skew                               | t <sub>SK,B</sub>    |        |          | 150                   | ps          |                                                                                                                                                                  |  |  |  |  |  |

|                                           |                      |        | DC       | O Mode Charac         | teristics   |                                                                                                                                                                  |  |  |  |  |  |

| Frequency Tuning Range                    | F <sub>RNG_DCO</sub> | -800   |          | +800                  | ppm         | Tuning via I2C or SPI                                                                                                                                            |  |  |  |  |  |

| Frequency Step Resolution                 | F <sub>RES_DCO</sub> |        | 0.023    |                       | ppt         | Increment/decrement 36-bit register                                                                                                                              |  |  |  |  |  |

| Frequency Tuning Clipping Resolution      | F <sub>CLP_DCO</sub> |        | 0.763    |                       | ppb         |                                                                                                                                                                  |  |  |  |  |  |

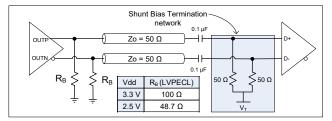

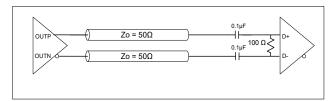

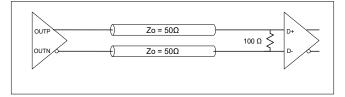

**Table 4. Electrical Characteristics – LVPECL** | See Figure 2 and Figure 3 for test setups. Current consumption only accounts for VDDO and output driver stage.

| Parameter                                                  | Symbol     | Min.      | Тур.       | Max.          | Unit      | Condition                                                                                                                                       |

|------------------------------------------------------------|------------|-----------|------------|---------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            |            | Curre     | ent Consun | nption, f = 1 | 156.25 MH | Ⅎz                                                                                                                                              |

| Current Consumption, Output<br>Enabled without Termination | Idd_oe_nt  | -         | _          | 25            | mA        | Excluding load termination current                                                                                                              |

| Current Consumption, Output Disabled without Termination   | ldd_od_nt  | -         | ı          | 13            | mA        | Excluding load termination current                                                                                                              |

| Current Consumption, Output                                | 14444      | -         | -          | 38            | mA        | Including load termination current as shown in Figure 24 for Vdd=3.3 V ±10% and R3=220 Ohms                                                     |

| Enabled with Termination 1                                 | Idd_oe_wt1 | -         | -          | 36            | mA        | Including load termination current as shown in Figure 24 for Vdd=2.5 V ±10% and R3=220 Ohms                                                     |

| Current Consumption Output                                 | ldd od ut1 | -         | ı          | 26            | mA        | Including load termination current as shown in Figure 24 for Vdd=3.3 V ±10%and R3=220 Ohms. Driver output is held at last clock output levels.  |

| Disabled with Termination 1                                | ldd_od_wt1 | -         | ı          | 24            | mA        | Including load termination current as shown in Figure 24 for Vdd=2.5 V ±10% and R3=220 Ohms. Driver output is held at last clock output levels. |

| Current Consumption, Output<br>Enabled with Termination 2  | Idd_oe_wt2 | -         | -          | 53            | mA        | Including load termination current. See Figure 25 for termination                                                                               |

| Current Consumption, Output Disabled with Termination 2    | Idd_od_wt2 | -         | ı          | 41            | mA        | Including load termination current. See Figure 25 for termination. Driver output is held at last clock output levels.                           |

|                                                            |            |           | Output     | Characteri    | stics     |                                                                                                                                                 |

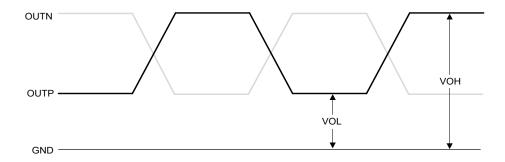

| Output High Voltage                                        | VOH        | Vdd-1.075 | Vdd-0.95   | Vdd-0.86      | V         | See Figure 12 for waveform                                                                                                                      |

| Output Low Voltage                                         | VOL        | Vdd-1.84  | Vdd-1.7    | Vdd-1.62      | V         | See Figure 12 for waveform                                                                                                                      |

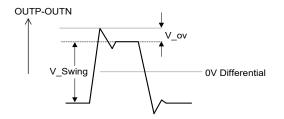

| Output Differential Voltage Swing                          | V_Swing    | 1.4       | _          | 1.8           | V         | See Figure 13 for waveform                                                                                                                      |

| Rise/Fall Time                                             | Tr, Tf     | -         | 210        | 300           | ps        | 20% to 80%. See Figure 13 for waveform                                                                                                          |

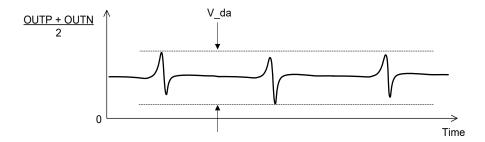

| Differential Asymmetry, peak-peak                          | V_da       | -         | -          | 85            | mV        | See Figure 15 for waveform                                                                                                                      |

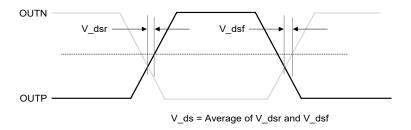

| Differential Skew, peak                                    | V_ds       | -         | -          | ±25           | ps        | See Figure 16 for waveform                                                                                                                      |

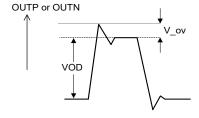

| Overshoot Voltage, peak                                    | V_ov       | -         | -          | 12            | %         | Measured as percent of V_Swing. See Figure 17 for waveform                                                                                      |

|                                                            |            | Powe      | r Supply N | oise Immur    | nity (VDD | 0)                                                                                                                                              |

| Paris Oranda Indiana di Iitta                              |            | _         | _          | 10            | fs/mV     | Power supply ripple from 10 kHz to 20 MHz                                                                                                       |

| Power Supply-Induced Jitter<br>Sensitivity                 | PSJS       | -         | -          | 8             | fs/mV     | Power supply ripple from 10 kHz to 20 MHz. Using RC power supply filter as shown in Figure 2                                                    |

| Power Supply Induced Phase                                 |            | -         | _          | -85           | dBc       | 50 mV peak-peak ripple on VDD                                                                                                                   |

| Power Supply-Induced Phase Noise                           | PSPN       | -         | -          | -90           | dBc       | 50 mV peak-peak ripple on VDD. Using RC power supply filter as shown in Figure 2                                                                |

**Table 5. Electrical Characteristics – FlexSwing** | See Figure 4 and Figure 5 for test setups. Current consumption only accounts for VDDO and output driver stage.

| Parameter                                                  | Symbol    | Min.      | Тур.              | Max.       | Unit      | Condition                                                                                                                                                                |

|------------------------------------------------------------|-----------|-----------|-------------------|------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            |           |           | Currer            | nt Consump | otion     |                                                                                                                                                                          |

| Current Consumption, Output<br>Enabled without Termination | Idd_oe_nt | -         | -                 | 25         | mA        | Excluding load termination current                                                                                                                                       |

| Current Consumption, Output Disabled without Termination   | Idd_od_nt | -         | ı                 | 13         | mA        | Excluding load termination current                                                                                                                                       |

| Current Consumption, Output                                | Idd oe wt | -         | ı                 | 35         | mA        | Including load termination current, for FlexSwing order code "ER". See Figure 24 for Vdd=3.3 V ±10% and R3=220 Ohms                                                      |

| Enabled with Termination                                   | idd_0e_wt | -         | -                 | 35         | mA        | Including load termination current, for FlexSwing order code "ER". See Figure 24 for Vdd=2.5 V ±10%, and R3=220 Ohms                                                     |

| Current Consumption Output                                 |           | -         | -                 | 23         | mA        | Including load termination current, for FlexSwing order code "ER". See Figure 24 for Vdd=3.3 V ±10% and R3=220 Ohms. Driver output is held at last clock output levels.  |

| Disabled with Termination                                  | Idd_od_wt | -         | code "ER". See Fi |            |           | Including load termination current, for FlexSwing order code "ER". See Figure 24 for Vdd=2.5 V ±10%, and R3=220 Ohms. Driver output is held at last clock output levels. |

|                                                            | •         |           | Output            | Characteri | stics     |                                                                                                                                                                          |

| Output High Voltage                                        | VOH       | VHn -0.13 | VHn               | VHn +0.1   | V         | See Figure 12 for waveform; Refer to Table 10 or Table 11 order codes for nominal VOH (i.e. VHn) values                                                                  |

| Output Low Voltage                                         | VOL       | VLn -0.13 | VLn               | VLn +0.12  | V         | See Figure 12 for waveform; Refer to Table 10 or Table 11 order codes for nominal VOL (i.e. VLn) values                                                                  |

| Output Differential Voltage Swing                          | V_Swing   | -0.2      | 2*( VHn-<br>VLn)  | +0.2       | V         | See Figure 13 for waveform                                                                                                                                               |

| Rise/Fall Time                                             | Tr, Tf    | -         | 250               | 300        | ps        | 20% to 80%. See Figure 13 for waveform                                                                                                                                   |

| Differential Asymmetry, peak-peak                          | V_da      | -         | ı                 | 100        | mV        | See Figure 15 for waveform                                                                                                                                               |

| Differential Skew, peak                                    | V_ds      | -         | -                 | ±25        | ps        | See Figure 16 for waveform                                                                                                                                               |

| Overshoot Voltage, peak                                    | V_ov      | _         | -                 | 12         | %         | Measured as percent of V_Swing. See Figure 17 for waveform                                                                                                               |

|                                                            |           | Pow       | er Supply         | Noise Imm  | unity (VD | DO)                                                                                                                                                                      |

| Device Comply Indicated Little                             |           | -         | -                 | 10         | fs/mV     | Power supply ripple from 10 kHz to 20 MHz. For FlexSwing order code "ER"                                                                                                 |

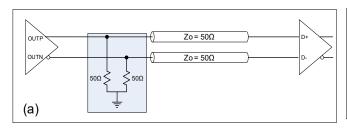

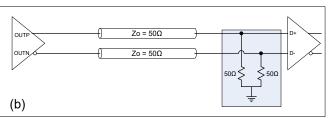

| Power Supply-Induced Jitter<br>Sensitivity                 | PSJS      | -         | -                 | 8          | fs/mV     | Power supply ripple from 10 kHz to 20 MHz. For FlexSwing order code "ER". Using RC power supply filter as shown in Figure 4                                              |

| Power Supply-Induced Phase                                 | DCDN      | -         | -                 | -85        | dBc       | 50 mV peak-peak ripple on VDD.<br>For FlexSwing order code "ER"                                                                                                          |

| Noise                                                      | PSPN      | -         | -                 | -90        | dBc       | 50 mV peak-peak ripple on VDD. For FlexSwing order code "ER". Using R C power supply filter as shown in Figure 4                                                         |

**Table 6. Electrical Characteristics – LVDS** | See Figure 6 and Figure 7 for test setups. Current consumption only accounts for VDDO and output driver stage.

| Parameter                                                  | Symbol    | Min.  | Тур.        | Max.        | Unit      | Condition                                                                                                             |

|------------------------------------------------------------|-----------|-------|-------------|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------|

|                                                            |           |       | Curren      | t Consump   | tion      |                                                                                                                       |

| Current Consumption, Output<br>Enabled without Termination | Idd_oe_nt | -     |             | 25          | mA        | Excluding load termination current                                                                                    |

| Current Consumption, Output Disabled without Termination   | Idd_od_nt | -     |             | 13          | mA        | Excluding load termination current                                                                                    |

| Current Consumption, Output<br>Enabled with Termination    | ldd_oe_wt | -     |             | 29          | mA        | Including load termination current. See Figure 28 for termination                                                     |

| Current Consumption Output Disabled with Termination       | ldd_od_wt | -     |             | 17          | mA        | Including load termination current. See Figure 28 for termination. Driver output is held at last clock output levels. |

|                                                            |           |       | Output      | Characteris | stics     |                                                                                                                       |

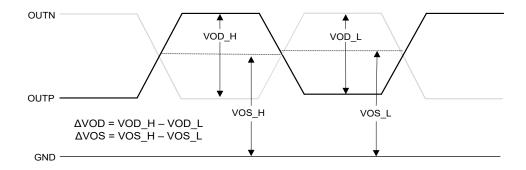

| Differential Output Voltage                                | VOD       | 250   | 360         | 450         | mV        | See Figure 14 for waveform                                                                                            |

| Delta VOD                                                  | ΔVOD      | 1     | -           | 50          | mV        | See Figure 14 for waveform                                                                                            |

|                                                            |           | 1.125 | 1.25        | 1.375       |           | See Figure 14 for waveform                                                                                            |

|                                                            |           | 1.0   |             | 1.05        |           | See Figure 14 for waveform VDDO = 1.8V                                                                                |

| Delta VOS                                                  | ΔVOS      | _     | ı           | 50          | mV        | See Figure 14 for waveform                                                                                            |

| Rise/Fall Time                                             | Tr, Tf    | -     | 220         | 300         | ps        | Measured 20% to 80% using Figure 28 for termination.<br>See Figure 13 for waveform                                    |

| Differential Asymmetry, peak-peak                          | V_da      | -     | -           | 50          | mV        | See Figure 15 for waveform                                                                                            |

| Differential Skew, peak                                    | V_ds      | _     | _           | ±25         | ps        | See Figure 16 for waveform                                                                                            |

| Overshoot Voltage, peak                                    | V_ov      | -     | ı           | 10          | %         | Measured as percent of VOD.<br>See Figure 18 for waveform                                                             |

|                                                            |           | Powe  | er Supply N | loise Immu  | nity (VDD | 00)                                                                                                                   |

| Power Supply-Induced Jitter                                | PSJS      | -     | -           | 10          | fs/mV     | Power supply ripple from 10 kHz to 20 MHz                                                                             |

| Sensitivity                                                | PSJS      | -     | -           | 8           | fs/mV     | Power supply ripple from 10 kHz to 20 MHz. Using RC power supply filter as shown in Figure 6                          |

| Power Supply-Induced Phase                                 | PSPN      | -     | ı           | -85         | dBc       | 50 mV peak-peak ripple on VDD                                                                                         |

| Noise                                                      | PSPN –    |       |             | -90         | dBc       | 50 mV peak-peak ripple on VDD. Using RC power supply filter as shown in Figure 6                                      |

**Table 7. Electrical Characteristics – HCSL** | See Figure 8 and Figure 9 for test setups. Current consumption only accounts for VDDO and output driver stage.

| Parameter                                                  | Symbol    | Min. | Тур.        | Max.       | Unit       | Condition                                                                                    |

|------------------------------------------------------------|-----------|------|-------------|------------|------------|----------------------------------------------------------------------------------------------|

|                                                            |           |      | Currer      | nt Consum  | ption      |                                                                                              |

| Current Consumption, Output<br>Enabled without Termination | Idd_oe_nt | _    | ı           | 25         | mA         | Excluding load termination current                                                           |

| Current Consumption, Output Disabled without Termination   | ldd_od_nt | 1    | 1           | 13         | mA         | Excluding load termination current                                                           |

|                                                            |           |      | Output      | Characteri | stics      |                                                                                              |

| Output High Voltage                                        | VOH       | 0.60 | 0.7         | 0.95       | V          | See Figure 12 for waveform                                                                   |

| Output Low Voltage                                         | VOL       | -0.1 | 0           | 0.1        | V          | See Figure 12 for waveform                                                                   |

| Output Differential Voltage Swing                          | V_Swing   | 1.1  | 1.4         | 1.6        | V          | See Figure 13 for waveform                                                                   |

| Rise/Fall Time                                             | Tr, Tf    | -    | 250         | 300        | ps         | Measured 20% to 80%.<br>See Figure 13 for waveform                                           |

| Differential Asymmetry, peak-peak                          | V_da      | 1    | _           | 65         | mV         | See Figure 15 for waveform                                                                   |

| Differential Skew, peak                                    | V_ds      | _    | ı           | ±25        | ps         | See Figure 16 for waveform                                                                   |

| Overshoot Voltage, peak                                    | V_ov      | ı    | ı           | 10         | %          | Measured as percent of V_Swing. See Figure 17 for waveform                                   |

|                                                            |           | Pow  | er Supply N | loise Immu | ınity (VDE | 00)                                                                                          |

| Power Supply-Induced Jitter                                |           | _    | ı           | 10         | fs/mV      | Power supply ripple from 10 kHz to 20 MHz                                                    |

| Sensitivity                                                | PSJS      | -    | -           | 8          | fs/mV      | Power supply ripple from 10 kHz to 20 MHz. Using RC power supply filter as shown in Figure 8 |

| Dower Supply Induced Phase                                 |           | _    | -           | -85        | dBc        | 50 mV peak-peak ripple on VDD                                                                |

| Power Supply-Induced Phase Noise                           | PSPN      | _    | -           | -90        | dBc        | 50 mV peak-peak ripple on VDD. Using RC power supply filter as shown in Figure 8             |

**Table 8. Electrical Characteristics – Low-Power HCSL** | See Figure 10 and Figure 11 for test setups. Current consumption only accounts for VDDO and output driver stage.

| Parameter                                                  | Symbol    | Min. | Тур.        | Max.       | Unit      | Condition                                                                                     |

|------------------------------------------------------------|-----------|------|-------------|------------|-----------|-----------------------------------------------------------------------------------------------|

|                                                            |           |      | Currer      | nt Consum  | otion     |                                                                                               |

| Current Consumption, Output<br>Enabled without Termination | ldd_oe_nt | -    | 1           | 25         | mA        | Excluding load termination current                                                            |

| Current Consumption, Output Disabled without Termination   | ldd_od_nt | -    | 1           | 13         | mA        | Excluding load termination current                                                            |

|                                                            |           |      | Output      | Character  | istics    |                                                                                               |

| Output High Voltage                                        | VOH       | -    | ı           | 1.1        | V         | See Figure 12 for waveform                                                                    |

| Output Low Voltage                                         | VOL       | -0.1 | 0           | 0.1        | V         | See Figure 12 for waveform                                                                    |

| Output Differential Voltage Swing                          | V_Swing   | 1.4  | 1.83        | 2.0        | V         | See Figure 13 for waveform                                                                    |

| Rise/Fall Time                                             | Tr, Tf –  |      | 250         | 300        | ps        | Measured 20% to 80%. See Figure 13 for waveform                                               |

| Differential Asymmetry, peak-peak                          | V_da      | -    | ı           | 85         | mV        | See Figure 15 for waveform                                                                    |

| Differential Skew, peak                                    | V_ds      | -    | ı           | ±30        | ps        | See Figure 16 for waveform                                                                    |

| Overshoot Voltage, peak                                    | V_ov      | -    | ı           | 10         | %         | Measured as percent of V_Swing. See Figure 17 for waveform                                    |

|                                                            |           | Pow  | er Supply I | Noise Immi | ınity (VD | DO)                                                                                           |

| Barrer Ormalia la direct di litteri                        |           | -    | 1           | 10         | fs/mV     | Power supply ripple from 10 kHz to 20 MHz                                                     |

| Power Supply-Induced Jitter<br>Sensitivity                 | PSJS      | -    | 1           | 8          | fs/mV     | Power supply ripple from 10 kHz to 20 MHz. Using RC power supply filter as shown in Figure 10 |

| Barrer Commission and Black                                |           | -    | ı           | -85        | dBc       | 50 mV peak-peak ripple on VDD                                                                 |

| Power Supply-Induced Phase<br>Noise                        | PSPN      | -    | ı           | -90        | dBc       | 50 mV peak-peak ripple on VDD. Using RC power supply filter as shown in Figure 10             |

**Table 9. Electrical Characteristics – Low-Voltage CMOS** | Current consumption only accounts for VDDO and output driver stage.

| Parameter                                  | Symbol  | Min.     | Тур.        | Max.          | Unit       | Condition                                                                                                              |

|--------------------------------------------|---------|----------|-------------|---------------|------------|------------------------------------------------------------------------------------------------------------------------|

|                                            |         |          | Currer      | nt Consump    | otion      |                                                                                                                        |

| Current Consumption, Output Enabled        | ldd_oe  | 1        | 1           | 14            | mA         |                                                                                                                        |

| Current Consumption, Output Disabled       | ldd_od  | 1        | -           | 12            | mA         |                                                                                                                        |

|                                            |         | Outpu    | t Charactei | ristics (Star | dard LVC   | CMOS)                                                                                                                  |

| Output High Voltage                        | VOH     | 90%      | ı           | -             | VDDO       | IOH = -4 mA, VDDO = 3.3 V                                                                                              |

| Output Low Voltage                         | VOL     | 1        | ı           | 10%           | VDDO       | IOL = 4 mA, VDDO = 3.3 V                                                                                               |

| Rise/Fall Time                             | Tr, Tf  | -        | ı           | 5             | ns         | Measured 20% to 80%, output frequency 20 MHz, load = 8 pF. SiT91213 has programmable options for rise-time & fall-time |

| Duty Cycle                                 |         | 45       | ı           | 55            | %          | Measured in percentage of clock period                                                                                 |

| Overshoot Voltage, peak                    | V_ov    | -        | ı           | 10            | %          | Measured as percent of difference between VOH and VOL                                                                  |

|                                            |         | Output C | Characteris | tics (Regula  | ated LVC   | MOS)                                                                                                                   |

| Output High Voltage Regulated Range        | VDDOreg | 0.9      | -           | VDDO-0.3      | ٧          | Regulated VOH can be programmed with up to 20 steps                                                                    |

| Output High Voltage Regulated Range        | VOH     | 90%      | _           | _             | VDDOreg    | IOH = -4 mA, VDDO = 3.3 V                                                                                              |

| Output Low Voltage                         | VOL     | -        | _           | 10%           | VDDreg     | IOL = 4 mA, VDDO = 3.3 V                                                                                               |

| Rise/Fall Time                             | Tr, Tf  | ı        | 0.4         | 0.6           | ns         | Measured 20% to 80%, output frequency 20 MHz, load = 8 pF. SiT91283 has programmable options for rise-time & fall-time |

| Overshoot Voltage, peak                    | V_ov    | -        | _           | 10            | %          | Measured as percent of difference between VOH and VOL                                                                  |

|                                            |         | Pow      | er Supply   | Noise Immu    | ınity (VDI | DO)                                                                                                                    |

| Power Supply-Induced Jitter<br>Sensitivity | PSJS    | _        |             | 20            | fs/mV      | Power supply ripple from 10 kHz to 20 MHz                                                                              |

| Power Supply-Induced Phase Noise           | PSPN    | _        | -           | -70           | dBc        | 50 mV peak-peak ripple on VDD                                                                                          |

### FlexSwing Configurations

A FlexSwing output-driver performs like LVPECL and additionally provides independent control of voltage swing and DC offset voltage levels. This simplifies interfacing with chipsets having non-standard input voltage requirements

and can eliminate all external source-bias resistors. FlexSwing supports power supply voltages from 1.71 V to 3.63 V, and the programmable VOH and VOL levels may be referenced to the voltage on either VDD or GND pins.

Table 10<sup>[6]</sup>. FlexSwing 2-digit Order Codes specifying VHn and VLn referenced to voltage on VDD pin

|     |          |                           |            |            |            |            |            |            |            |            |            |            | ٧          | 'Ln        |            |            |            |            |                                     |            |             |            |            |            |

|-----|----------|---------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------------------------------------|------------|-------------|------------|------------|------------|

|     |          |                           | Α          | В          | С          | D          | E          | F          | G          | Н          | J          | К          | L          | М          | N          | P          | Q          | R          | S                                   | Т          | U           | V          | W          | х          |

|     |          | order Code<br>'_Swing (V) | Vdd-2.31V  | Vdd-2.26V  | Vdd-2.21V  | Vdd-2.16V  | Vdd-2.11V  | Vdd-2.06V  | Vdd-2.01V  | Vdd-1.96V  | Vdd-1.91V  | Vdd-1.86V  | Vdd-1.82V  | Vdd-1.77V  | Vdd-1.72V  | Vdd-1.67V  | Vdd-1.62V  | Vdd-1.57V  | Vdd-1.52V<br>Vdd-1.47V<br>Vdd-1.37V |            | Vdd-1.32V   | vdd-1.28V  |            |            |

|     |          |                           | >          | Š          | Š          | Š          | >          | Š          | Š          | Š          | -          | -          | -          | -          | -          | -          | -          | -          | -                                   | -          | -           | -          | -          | _          |

|     | Α        |                           |            |            |            |            |            |            |            |            | AJ<br>1.94 | AK<br>1.86 | AL<br>1.77 | AM<br>1.69 | AN<br>1.61 | AP<br>1.52 | AQ<br>1.44 | AR<br>1.35 | AS<br>1.27                          | AT<br>1.18 | AU<br>1.10  | AV<br>1.01 | AW<br>0.93 | AX<br>0.85 |

|     | В        |                           |            |            |            |            |            |            |            |            | BJ         | ВК         | BL         | BM         | BN         | ВР         | BQ         | BR         | BS                                  | BT         | BU          | BV         | BW         | ВХ         |

|     | _        |                           |            |            |            |            |            |            |            | 1.94       | 1.86       | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18                                | 1.10       | 1.01        | 0.93       | 0.85       | 0.76       |

|     | С        |                           |            |            |            |            |            |            | 4.04       | 4.00       | CJ         | CK         | CL         | CM         | CN         | CP         | cq         | CR         | CS                                  | CT         | CU          | CV         | CW         | СХ         |

|     | -        |                           |            |            |            |            |            |            | 1.94       | 1.86       | 1.77<br>DJ | 1.69<br>DK | 1.61<br>DL | 1.52<br>DM | 1.44<br>DN | 1.35<br>DP | 1.27<br>DQ | 1.18<br>DR | 1.10<br>DS                          | 1.01<br>DT | 0.93<br>DU  | 0.85<br>DV | 0.76<br>DW | 0.68<br>DX |

|     | D        |                           |            |            |            |            |            | 1.94       | 1.86       | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01                                | 0.93       | 0.85        | 0.76       | 0.68       | 0.59       |

|     | Е        |                           |            |            |            |            |            |            |            |            | EJ         | EK         | EL         | EM         | EN         | EP         | EQ         | ER         | ES                                  | ET         | EU          | EV         | EW         | EX         |

|     |          |                           |            |            |            |            | 1.94       | 1.86       | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.014      | 0.93                                | 0.85       | 0.76        | 0.68       | 0.59       | 0.51       |

|     | F        |                           |            |            |            |            |            |            |            |            | FJ         | FK         | FL         | FM         | FN         | FP         | FQ         | FR         | FS                                  | FT         | FU          | FV         | FW         |            |

|     |          |                           |            |            |            | 1.94       | 1.86       | 1.77       | 1.69       | 1.61<br>GH | 1.52<br>GJ | 1.44<br>GK | 1.35<br>GL | 1.27<br>GM | 1.18<br>GN | 1.10<br>GP | 1.01       | 0.93<br>GR | 0.85<br>GS                          | 0.76<br>GT | 0.676<br>GU | 0.59<br>GV | 0.51       | 0.42       |

|     | G        |                           |            |            | 1.94       | 1.86       | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | GQ<br>0.93 | 0.85       | 0.76                                | 0.68       | 0.59        | 0.51       | 0.42       | 0.34       |

|     | <u>.</u> |                           |            |            | 1.54       | 1.00       | 1.77       | 1.03       | HG         | HH         | HJ         | HK         | HL         | HM         | HN         | HP         | HQ         | HR         | HS                                  | HT         | HU          | 0.31       | 0.42       | 0.54       |

|     | Н        |                           |            | 1.94       | 1.86       | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68                                | 0.59       | 0.51        | 0.42       | 0.34       | 0.25       |

|     | J        |                           |            |            |            |            |            | JF         | JG         | JH         | II         | JK         | JL         | JM         | JN         | JP         | JQ         | JR         | JS                                  | JT         |             |            |            |            |

|     | _        |                           | 1.94       | 1.86       | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59                                | 0.51       | 0.42        | 0.34       | 0.25       |            |

|     | к        | 8/2                       | 4.00       | 4          | 4.60       | 4.64       | KE         | KF         | KG         | KH         | KJ         | KK         | KL         | KM         | KN         | KP         | KQ         | KR         | KS                                  | 0.43       | 0.24        | 0.35       |            |            |

|     |          | VLn + V_Swing /           | 1.86       | 1.77       | 1.69       | 1.61<br>LD | 1.52<br>LE | 1.44<br>LF | 1.35<br>LG | 1.27<br>LH | 1.18<br>U  | 1.10<br>LK | 1.01<br>LL | 0.93<br>LM | 0.85<br>LN | 0.76<br>LP | 0.68<br>LQ | 0.59<br>LR | 0.51                                | 0.42       | 0.34        | 0.25       |            |            |

| VHn | L        | ر<br>ا<br>ا               | 1.77       | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59       | 0.51       | 0.42                                | 0.34       | 0.25        |            |            |            |

|     |          | +                         |            |            | MC         | MD         | ME         | MF         | MG         | МН         | MJ         | MK         | ML         | MM         | MN         | MP         | MQ         |            |                                     |            |             |            |            |            |

|     | М        | ₹                         | 1.69       | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59       | 0.51       | 0.42       | 0.34                                | 0.25       |             |            |            |            |

|     | N        |                           |            | NB         | NC         | ND         | NE         | NF         | NG         | NH         | NJ         | NK         | NL         | NM         | NN         | NP         |            |            |                                     |            |             |            |            |            |

|     |          |                           | 1.61       | 1.52       | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59       | 0.51       | 0.42       | 0.34       | 0.25                                |            |             |            |            |            |

|     | Р        |                           | PA<br>1.52 | PB<br>1.44 | PC<br>1.35 | PD<br>1.27 | PE<br>1.18 | PF<br>1.10 | PG<br>1.01 | PH<br>0.93 | PJ<br>0.85 | PK<br>0.76 | PL<br>0.68 | PM<br>0.59 | PN<br>0.51 | 0.42       | 0.34       | 0.25       |                                     |            |             |            |            |            |

|     | Ļ        |                           | QA         | QB         | QC         | QD         | QE         | QF         | QG         | QH         | QJ         | QK         | QL         | QM         | 0.31       | 0.72       | 0.54       | -0.25      |                                     |            |             |            |            |            |

|     | Q        |                           | 1.44       | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59       | 0.51       | 0.42       | 0.34       | 0.25       |            |                                     |            |             |            |            |            |

|     | R        |                           | RA         | RB         | RC         | RD         | RE         | RF         | RG         | RH         | RJ         | RK         | RL         |            |            |            |            |            | Suppl                               | y Voltag   | e Ava       | ilable C   | olors      |            |

|     |          |                           | 1.35       | 1.27       | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59       | 0.51       | 0.42       | 0.34       | 0.25       |            |            | 1.8                                 | 3V±5%      | No          | t Suppo    | rted       |            |

|     | s        |                           | SA<br>1.27 | SB<br>1.18 | SC<br>1.10 | SD<br>1.01 | SE<br>0.93 | SF<br>0.85 | SG<br>0.76 | SH<br>0.68 | SJ<br>0.59 | SK<br>0.51 | 0.42       | 0.34       | 0.25       |            |            |            | 1.71V                               | to 3.63    | V No        | t Suppo    | rted       |            |

|     | H        |                           | TA         | 1.18<br>TB | TC         | TD         | TE         | U.85       | TG         | TH         | 0.59<br>TJ | 0.51       | 0.42       | 0.34       | 0.23       |            |            |            |                                     | V±10%      |             | Blue       |            |            |

|     | Т        |                           | 1.18       | 1.10       | 1.01       | 0.93       | 0.85       | 0.76       | 0.68       | 0.59       | 0.51       | 0.42       | 0.34       | 0.25       | l          |            |            |            |                                     | V±10%      | Blu         |            | Red        |            |

|     | υ        |                           | UA         | UB         | UC         | UD         | UE         | UF         | UG         | UH         |            |            |            |            |            |            |            |            | _                                   | to 3.63    | V           | Blue       |            |            |